- 品牌

- Nvidia

- 型号

- H100

- 磁盘阵列

- Raid10

- CPU类型

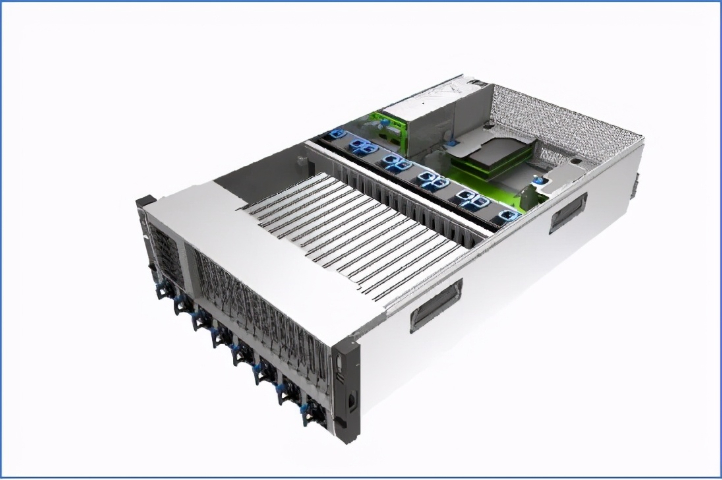

- Intel Platinum 8558 48 核

- CPU主频

- 2.10

- 内存类型

- 64G

- 硬盘容量

- Samsung PM9A3 7.6TB NVMe *8

- 厂家

- SuperMicro

- 标配CPU个数

- 2个

- 最大CPU个数

- 4个

- 内存容量

- 64G*32

- GPU

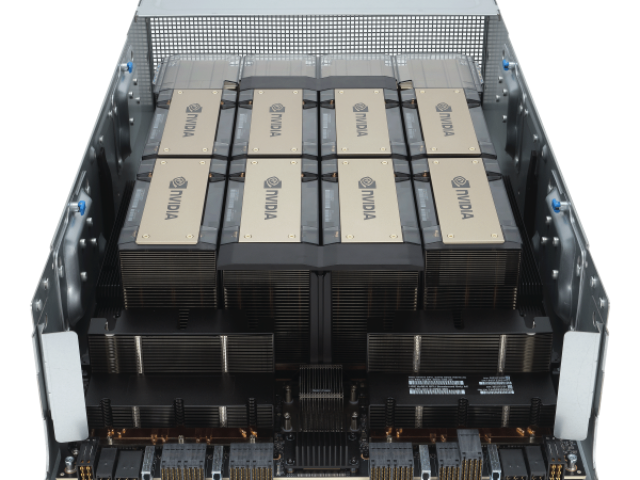

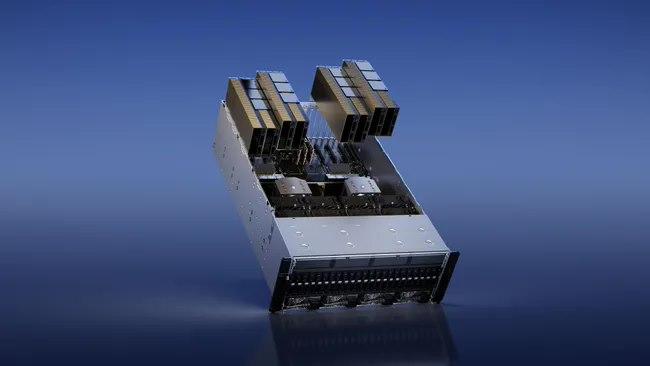

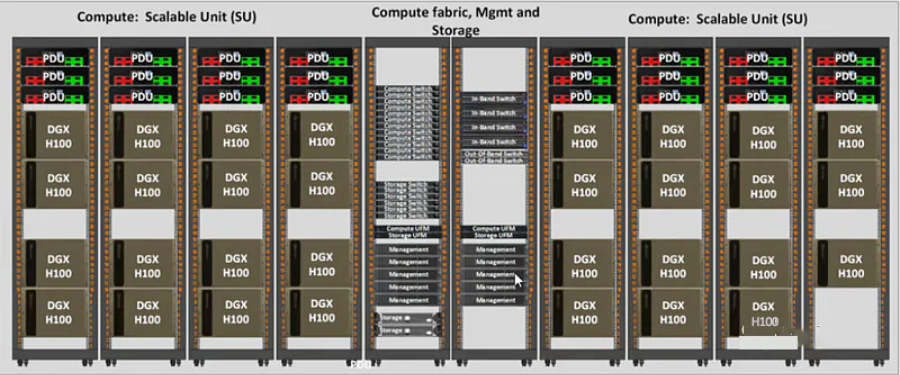

- 8 H100 80GB NVlink

使用TSMC4nm工艺定制800亿个晶体管,814mm²芯片面积。NVIDIAGraceHopperSuperchipCPU+GPU架构NVIDIAGraceCPU:利用ARM架构的灵活性,创建了从底层设计的CPU和服务器架构,用于加速计算。H100:通过NVIDIA的超高速片间互连与Grace配对,能提供900GB/s的带宽,比PCIeGen5快了7倍目录H100GPU主要特征基于H100的系统和板卡H100张量架构FP8数据格式用于加速动态规划(“DynamicProgramming”)的DPX指令L1数据cache和共享内存结合H100GPU层次结构和异步性改进线程块集群(ThreadBlockClusters)分布式共享内存(DSMEM)异步执行H100HBM和L2cache内存架构H100HBM3和HBM2eDRAM子系统H100L2cache内存子系统RAS特征第二代安全MIGTransformer引擎第四代NVLink和NVLink网络第三代NVSwitch新的NVLink交换系统PCIeGen5安全性增强和保密计算H100video/IO特征H100GPU主要特征新的流式多处理器(StreamingMultiprocessor,SM)第四代张量:片间通信速率提高了6倍(包括单个SM加速、额外的SM数量、更高的时钟);在等效数据类型上提供了2倍的矩阵乘加。MatrixMultiply-Accumulate,MMA)计算速率,相比于之前的16位浮点运算,使用新的FP8数据类型使速率提高了4倍。H100 GPU 降价特惠,先到先得。CPUH100GPU价格

这些线程可以使用SM的共享内存与快速屏障同步并交换数据。然而,随着GPU规模超过100个SM,计算程序变得更加复杂,线程块作为编程模型中表示的局部性单元不足以大化执行效率。Cluster是一组线程块,它们被保证并发调度到一组SM上,其目标是使跨多个SM的线程能够有效地协作。GPC:GPU处理集群,是硬件层次结构中一组物理上总是紧密相连的子模块。H100中的集群中的线程在一个GPC内跨SM同时运行。集群有硬件加速障碍和新的访存协作能力,在一个GPC中SM的一个SM-to-SM网络提供集群中线程之间快速的数据共享。分布式共享内存(DSMEM)通过集群,所有线程都可以直接访问其他SM的共享内存,并进行加载(load)、存储(store)和原子(atomic)操作。SM-to-SM网络保证了对远程DSMEM的快速、低延迟访问。在CUDA层面,集群中所有线程块的所有DSMEM段被映射到每个线程的通用地址空间中。使得所有DSMEM都可以通过简单的指针直接引用。DSMEM传输也可以表示为与基于共享内存的障碍同步的异步复制操作,用于**完成。异步执行异步内存拷贝单元TMA(TensorMemoryAccelerator)TMA可以将大块数据和多维张量从全局内存传输到共享内存,反义亦然。使用一个copydescriptor。SingaporeH100GPU现货H100 GPU 拥有 8192 个 CUDA。

L2CacheHBM3内存控制器GH100GPU的完整实现8GPUs9TPCs/GPU(共72TPCs)2SMs/TPC(共144SMs)128FP32CUDA/SM4个第四代张量/SM6HBM3/HBM2e堆栈,12个512位内存控制器60MBL2Cache第四代NVLink和PCIeGen5H100SM架构引入FP8新的Transformer引擎新的DPX指令H100张量架构专门用于矩阵乘和累加(MMA)数学运算的高性能计算,为AI和HPC应用提供了开创性的性能。H100中新的第四代TensorCore架构提供了每SM的原始稠密和稀疏矩阵数学吞吐量的两倍支持FP8、FP16、BF16、TF32、FP64、INT8等MMA数据类型。新的TensorCores还具有更**的数据管理,节省了高达30%的操作数交付能力。FP8数据格式与FP16相比,FP8的数据存储需求减半,吞吐量提高一倍。新的TransformerEngine(在下面的章节中进行阐述)同时使用FP8和FP16两种精度,以减少内存占用和提高性能,同时对大型语言和其他模型仍然保持精度。用于加速动态规划(“DynamicProgramming”)的DPX指令新引入的DPX指令为许多DP算法的内循环提供了高等融合操作数的支持,使得动态规划算法的性能相比于AmpereGPU高提升了7倍。L1数据cache和共享内存结合将L1数据cache和共享内存功能合并到单个内存块中简化了编程。

H100中新的第四代TensorCore架构提供了每SM的原始稠密和稀疏矩阵数学吞吐量的两倍支持FP8、FP16、BF16、TF32、FP64、INT8等MMA数据类型。新的TensorCores还具有更**的数据管理,节省了高达30%的操作数交付能力。FP8数据格式与FP16相比,FP8的数据存储需求减半,吞吐量提高一倍。新的TransformerEngine(在下面的章节中进行阐述)同时使用FP8和FP16两种精度,以减少内存占用和提高性能,同时对大型语言和其他模型仍然保持精度。用于加速动态规划(“DynamicProgramming”)的DPX指令新引入的DPX指令为许多DP算法的内循环提供了高等融合操作数的支持,使得动态规划算法的性能相比于AmpereGPU高提升了7倍。L1数据cache和共享内存结合将L1数据cache和共享内存功能合并到单个内存块中简化了编程,减少了达到峰值或接近峰值应用性能所需的调优;为这两种类型的内存访问提供了佳的综合性能。H100GPU层次结构和异步性改进关键数据局部性:将程序数据尽可能的靠近执行单元异步执行:寻找的任务与内存传输和其他事物重叠。目标是使GPU中的所有单元都能得到充分利用。线程块集群(ThreadBlockClusters)提出背景:线程块包含多个线程并发运行在单个SM上。H100 GPU 的双精度浮点计算能力为 9.7 TFLOPS。

以优化内存和缓存的使用和性能。H100HBM3和HBM2eDRAM子系统带宽性能H100L2cache采用分区耦合结构(partitionedcrossbarstructure)对与分区直接相连的GPC中的子模块的访存数据进行定位和高速缓存。L2cache驻留控制优化了容量利用率,允许程序员有选择地管理应该保留在缓存中或被驱逐的数据。内存子系统RAS特征RAS:Reliability,Av**lable,Serviceability(可靠性,可获得性)ECC存储弹性(MemoryResiliency)H100HBM3/2e存储子系统支持单纠错双检错(SECDED)纠错码(ECC)来保护数据。H100的HBM3/2e存储器支持"边带ECC",其中一个与主HBM存储器分开的小的存储区域用于ECC位内存行重映射H100HBM3/HBM2e子系统可以将产生错误ECC码的内存单元置为失效。并使用行重映射逻辑将其在启动时替换为保留的已知正确的行每个HBM3/HBM2e内存块中的若干内存行被预留为备用行,当需要替换被判定为坏的行时可以被。第二代安全MIGMIG技术允许将GPU划分为多达7个GPU事件(instance),以优化GPU利用率,并在不同客户端(例如VM、容器和进程等)之间提供一个被定义的QoS和隔离,在为客户端提供增强的安全性和保证GPU利用率之外,还确保一个客户端不受其他客户端的工作和调度的影响。H100 GPU 促销优惠,赶快购买。上海80GH100GPU

H100 GPU 适用于虚拟现实开发。CPUH100GPU价格

ITMALL.sale 始终坚持以客户为中心的服务理念,不断提升自身的服务水平和产品质量。通过建立严格的质量控制体系,ITMALL.sale 确保每一台 H100 GPU 产品都经过严格检测,确保性能稳定和可靠。ITMALL.sale 还与多家企业建立了长期合作关系,凭借良好的信誉和质量的服务赢得了客户的信赖。ITMALL.sale 的目标是成为 H100 GPU 市场的,为客户提供质量的产品和服务,助力客户业务的快速发展。ITMALL.sale 以其质量的服务和产品在市场上赢得了良好的口碑。作为 H100 GPU 的专业代理商,ITMALL.sale 不仅能够提供具有竞争力的价格,还能够确保产品的质量和可靠性。通过与 NVIDIA 的紧密合作,ITMALL.sale 能够及时获取的产品信息和技术更新,为客户提供的 H100 GPU 产品和技术解决方案。无论是企业级客户还是个人用户,都能够在 ITMALL.sale 找到满足其需求的 H100 GPU 产品和服务。CPUH100GPU价格

- 技嘉H100GPU货期 2024-11-15

- 硬盘H100GPU优惠 2024-11-15

- Dubai戴尔H100GPU 2024-11-15

- LenovoH100GPU distributor 2024-11-15

- 北京H100GPU 2024-11-15

- 英伟达H100GPU货期 2024-11-15

- NVLINKH100GPU list price 2024-11-14

- QatarH100GPU stock 2024-11-14

- 河南H100GPU库存 2024-11-14

- 广东H100GPU 2024-11-14

- 技嘉H100GPU多少钱 2024-11-14

- CPUH100GPU多少钱 2024-11-14