- 品牌

- 士兰微,上海贝岭,新洁能,必易微

- 型号

- 10

- 制式

- 圆插头,扁插头

MOSFET的可靠性受电路设计、工作环境及器件特性共同影响,常见失效风险需针对性防护。首先是栅极氧化层击穿:因氧化层极薄(只几纳米),若Vgs超过额定值(如静电放电、驱动电压异常),易导致不可逆击穿。防护措施包括:栅源之间并联TVS管或稳压管钳位电压;焊接与操作时采取静电防护(如接地手环、离子风扇);驱动电路中串联限流电阻,限制栅极电流。其次是热失效:MOSFET工作时的导通损耗、开关损耗会转化为热量,若结温Tj超过较大值,会导致性能退化甚至烧毁。需通过合理散热设计解决:选择低Rds(on)器件减少损耗;搭配散热片、导热垫降低热阻;在电路中加入过温保护(如NTC热敏电阻、芯片内置过热检测),温度过高时关断器件。此外,雪崩击穿也是风险点:当Vds瞬间超过击穿电压时,漏极电流急剧增大,产生雪崩能量,需选择雪崩能量Eas足够大的器件,并在电路中加入RC吸收网络,抑制电压尖峰。士兰微 SVF4N60F MOSFET 性价比出众,广受小家电厂商青睐。常见MOS什么价格

在5G通信领域,MOSFET(尤其是射频MOSFET与GaNMOSFET)凭借优异的高频性能,成为基站射频前端的主要点器件。5G基站需处理更高频率的信号(Sub-6GHz与毫米波频段),对器件的线性度、噪声系数与功率密度要求严苛。

射频MOSFET通过优化栅极结构(如采用多栅极设计)与材料(如GaN),可在高频下保持低噪声系数(通常低于1dB)与高功率附加效率(PAE,可达60%以上),减少信号失真与能量损耗。在基站功率放大器(PA)中,GaNMOSFET能在毫米波频段输出更高功率(单管可达数十瓦),且体积只为传统硅基器件的1/3,可明显缩小基站体积,降低部署成本。此外,5G基站的大规模天线阵列(MassiveMIMO)需大量小功率射频MOSFET,其高集成度与一致性可确保各天线单元的信号同步,提升通信质量。未来,随着5G向6G演进,对MOSFET的频率与功率密度要求将进一步提升,推动更先进的材料与结构研发。 质量MOS销售公司瑞阳微 MOSFET 具备低导通电阻特性,助力电源设备节能降耗。

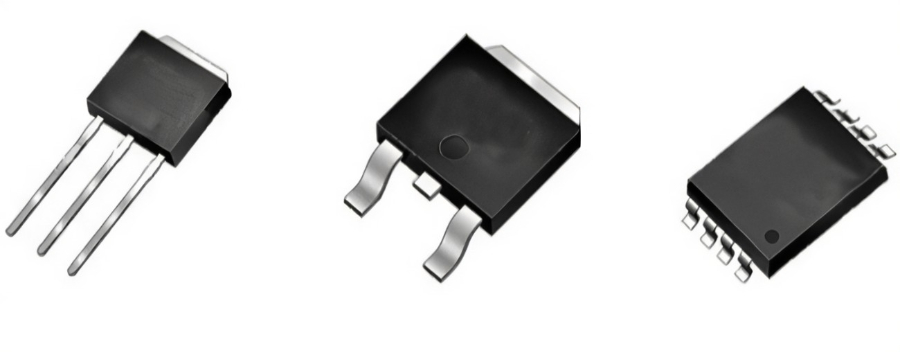

MOS管(金属-氧化物-半导体场效应晶体管)分为n沟道MOS管(NMOS)和p沟道MOS管(PMOS),其工作原理主要基于半导体的导电特性以及电场对载流子的控制作用,以下从结构和工作机制方面进行介绍:结构基础NMOS:以一块掺杂浓度较低的P型硅半导体薄片作为衬底,在P型硅表面的两侧分别扩散两个高掺杂浓度的N+区,这两个N+区分别称为源极(S)和漏极(D),在源极和漏极之间的P型硅表面覆盖一层二氧化硅(SiO₂)绝缘层,在绝缘层上再淀积一层金属铝作为栅极(G)。

这样就形成了一个金属-氧化物-半导体结构,在源极和衬底之间以及漏极和衬底之间都形成了PN结。PMOS:与NMOS结构相反,PMOS的衬底是N型硅,源极和漏极是P+区,栅极同样是通过绝缘层与衬底隔开。工作机制以NMOS为例截止区:当栅极电压VGS小于阈值电压VTH时,在栅极下方的P型衬底表面形成的是耗尽层,没有反型层出现,源极和漏极之间没有导电沟道,此时即使在漏极和源极之间加上电压VDS,也只有非常小的反向饱和电流(漏电流)通过,MOS管处于截止状态,相当于开关断开。

MOS 的性能特点呈现鲜明的场景依赖性,其优缺点在不同应用场景中被放大或弥补。重心优点包括:一是电压驱动特性,输入阻抗极高(10^12Ω 以上),栅极几乎不消耗电流,驱动电路简单、成本低,相比电流驱动的 BJT 优势明显;二是开关速度快,纳秒级的开关时间使其适配 100kHz 以上的高频场景,远超 IGBT 的开关速度;三是集成度高,平面结构与成熟工艺支持超大规模集成,单芯片可集成数十亿颗 MOS,是集成电路的重心单元;四是功耗低,低导通电阻与低漏电流结合,在消费电子、便携设备中能有效延长续航。其缺点也较为突出:一是耐压能力有限,传统硅基 MOS 的击穿电压多在 1500V 以下,无法适配特高压、超大功率场景(需依赖 IGBT 或宽禁带 MOS);二是通流能力相对较弱,大电流应用中需多器件并联,增加电路复杂度;三是抗静电能力差,栅极绝缘层极薄(纳米级),易被静电击穿,需额外做 ESD 防护设计。因此,MOS 更适配高频、低压、中大功率场景,与 IGBT、SiC 器件形成应用互补。瑞阳微 MOSFET 品质有保障,赢得众多长期合作客户的认可与信赖。

MOS 的广泛应用离不开 CMOS(互补金属 - 氧化物 - 半导体)技术的支撑,两者协同构成了现代数字集成电路的基础。CMOS 技术的重心是将 NMOS 与 PMOS 成对组合,形成逻辑门电路(如与非门、或非门),利用两种器件的互补特性实现低功耗逻辑运算:当 NMOS 导通时 PMOS 关断,反之亦然,整个逻辑操作过程中几乎无静态电流,只在开关瞬间产生动态功耗。这种结构不仅大幅降低了集成电路的功耗,还提升了抗干扰能力与逻辑稳定性,成为手机芯片、电脑 CPU、FPGA、MCU 等数字芯片的主流制造工艺。例如,一个基本的 CMOS 反相器由一只 NMOS 和一只 PMOS 组成,输入高电平时 NMOS 导通、PMOS 关断,输出低电平;输入低电平时则相反,实现信号反相。CMOS 技术与 MOS 器件的结合,支撑了集成电路集成度的指数级增长(摩尔定律),从早期的数千个晶体管到如今的数百亿个晶体管,推动了电子设备的微型化、高性能化与低功耗化,是信息时代发展的重心技术基石。士兰微 SVFTN65F MOSFET 热稳定性优异,适合长期高负荷工作环境。哪里有MOS智能系统

士兰微 SFR 系列快恢复二极管搭配 MOSFET,优化逆变器电路性能。常见MOS什么价格

MOSFET的栅极电荷Qg是驱动电路设计的关键参数,直接影响驱动功率与开关速度,需根据Qg选择合适的驱动芯片与外部元件。栅极电荷是指栅极从截止电压到导通电压所需的总电荷量,包括输入电容Ciss的充电电荷与米勒电容Cmiller的耦合电荷(Cmiller=Cgd,栅漏电容)。

Qg越大,驱动电路需提供的充放电电流越大,驱动功率(P=Qg×f×Vgs,f为开关频率)越高,若驱动能力不足,会导致开关时间延长,开关损耗增大。例如,在1MHz开关频率下,Qg=100nC、Vgs=12V的MOSFET,驱动功率约为1.2W,需选择输出电流大于100mA的驱动芯片。此外,Qg的组成也需关注:米勒电荷Qgd占比过高(如超过30%),会导致开关过程中栅压出现振荡,需通过RC吸收电路抑制。在高频应用中,需优先选择低Qg的MOSFET(如射频MOSFET的Qg通常小于10nC),同时搭配低输出阻抗的驱动芯片,确保快速充放电,降低驱动损耗。 常见MOS什么价格

MOS管(金属-氧化物-半导体场效应晶体管)分为n沟道MOS管(NMOS)和p沟道MOS管(PMOS),其工作原理主要基于半导体的导电特性以及电场对载流子的控制作用,以下从结构和工作机制方面进行介绍:结构基础NMOS:以一块掺杂浓度较低的P型硅半导体薄片作为衬底,在P型硅表面的两侧分别扩散两个高掺杂浓度的N+区,这两个N+区分别称为源极(S)和漏极(D),在源极和漏极之间的P型硅表面覆盖一层二氧化硅(SiO₂)绝缘层,在绝缘层上再淀积一层金属铝作为栅极(G)。 这样就形成了一个金属-氧化物-半导体结构,在源极和衬底之间以及漏极和衬底之间都形成了PN结。PMOS:与NMOS结构相反,P...

- 进口MOS代理商 2026-03-19

- 使用MOS发展趋势 2026-03-19

- 优势MOS生产厂家 2026-03-19

- 高科技MOS哪家便宜 2026-03-19

- 哪些是MOS销售厂 2026-03-19

- 低价MOS哪里买 2026-03-18

- 新能源MOS定做价格 2026-03-18

- 本地MOS发展趋势 2026-03-18

- 机电MOS价格信息 2026-03-18

- 自动MOS平均价格 2026-03-18

- 进口MOS代理商 03-19

- 使用MOS发展趋势 03-19

- 应用IGBT新报价 03-19

- 优势MOS生产厂家 03-19

- 高科技MOS哪家便宜 03-19

- 哪些是MOS销售厂 03-19

- 低价MOS哪里买 03-18

- 使用IGBT出厂价 03-18

- 新能源MOS定做价格 03-18

- 使用IGBT销售厂家 03-18