- 品牌

- 上海伟诺

- 型号

- 伟诺

- 适用行业

- 半导体

- 版本类型

- 网络版

- 语言版本

- 简体中文版

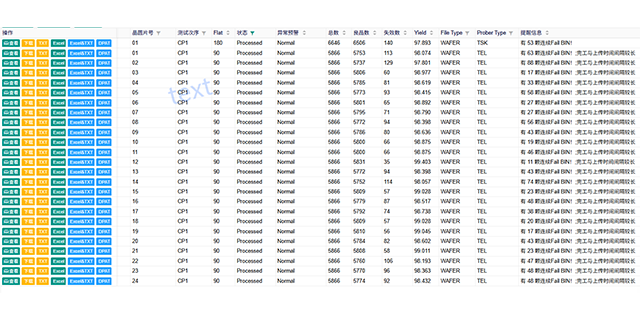

在封测工厂的日常运营中,良率波动往往源于测试数据分散、格式不一或异常信息未被及时识别。YMS系统自动对接ETS88、93k、J750、Chroma等主流Tester平台,高效采集stdf、csv、log、txt等多种格式的原始测试数据,并完成重复性检测、缺失值识别与异常数据过滤,确保后续分析基于准确、完整的数据基础。通过标准化数据库对数据统一分类,系统支持从时间序列追踪良率趋势,或从晶圆区域对比缺陷分布,快速定位工艺偏差。SYL与SBL参数的自动计算与卡控机制,进一步强化了质量防线。灵活的报表工具可按模板生成日报、周报、月报,并导出为PPT、Excel或PDF,满足从产线到管理层的信息需求。上海伟诺信息科技有限公司自2019年成立以来,持续深耕半导体软件领域,其YMS系统已成为封测企业实现质量闭环管理的重要支撑。参数漂移趋势在PAT分析中清晰呈现,实现早期风险预警。自动化Mapping Inkless的目的

企业在评估测封良率管理系统投入时,关注的是功能覆盖度与长期服务保障。YMS提供模块化配置,支持根据实际使用的Tester类型(如ETS364、Juno、AMIDA、CTA8280等)和数据格式(包括stdf、jdf、log等)灵活调整功能组合。系统不仅完成数据自动清洗与整合,还通过标准化数据库实现时间趋势、区域对比及缺陷聚类的多维分析。SYL与SBL的自动计算与阈值卡控,为封测过程设置动态质量防线。报价策略基于定制化程度与服务范围,确保企业在合理预算内获得高性价比解决方案。配套的售前咨询、售中方案优化与售后标准化服务,保障系统稳定运行与持续演进。上海伟诺信息科技有限公司以透明定价与完整服务体系,帮助客户实现良率管理的可持续提升。江西半导体GDBCMapping Over Ink处理通过空间分析有效识别外观损伤引起的隐性失效,提升可靠性。

芯片制造对良率控制的精度要求极高,YMS系统为此提供了从数据采集到根因分析的一站式解决方案。系统兼容多种测试平台输出的多格式文件,自动完成数据清洗与整合,确保从晶圆到单颗芯片的全链路数据一致性。通过关联WAT、CP、FT等阶段的关键参数,系统可精确识别导致良率下降的工艺或设计问题,并以图表形式展现芯片级缺陷分布与趋势变化。灵活的报表引擎支持按周期自动生成分析简报,便于跨部门协同与持续改进。这种精细化的数据治理能力,使企业在激烈竞争中保持质量优势。上海伟诺信息科技有限公司致力于用专业软件能力赋能中国半导体产业,其YMS系统已成为多家客户提升产品竞争力的重要工具。

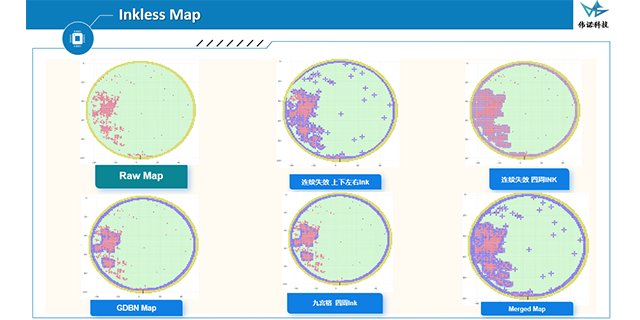

Mapping Over Ink是一套在晶圆测试(CP)后,对电性测试图谱进行智能分析、处理,并直接驱动探针台对特定芯片进行喷墨打点的自动化系统。它将各种分析算法(如ZPAT, GDBN)得出的“失效判定”转化为物理世界中的行动——将不良品标记出来,使其在后续封装中被剔除。其重点是预见性地剔除所有潜在缺陷芯片,而不仅是那些已经明确失效的。也是提升芯片零缺陷的一种重要方式。

上海伟诺信息科技有限公司作为半导体测试领域的解决方案供应商,致力于为国内外半导体设计公司与晶圆测试厂提供一站式的 Mapping Over Ink 整体解决方案。我们的平台集成了业界前沿、专业的数据分析与处理模块,旨在通过多重维度的智能筛选,构筑起一道安全的质量防线,有效地提升用户的晶圆测试质量与产品可靠性。 Mapping Inkless特别适用于洁净度要求高的车规级场景,保障晶圆表面完整性。

一套高效的良率管理系统开发方案,必须根植于真实生产场景的数据流与决策链。YMS方案覆盖从ETS88、93k、J750等Tester平台自动采集stdf、csv、log等多格式数据,到解析、清洗、整合的完整链路,确保数据源头的完整性与一致性。在此基础上,系统构建标准化数据库,实现对良率信息的统一分类与高效调用。分析层面,方案强调时间序列下的良率波动追踪与晶圆空间维度的缺陷聚类,结合WAT、CP、FT参数变化,形成从现象到根因的完整证据链。SYL与SBL的自动卡控机制嵌入关键控制点,实现预防性质量管理。同时,报表引擎支持按需生成周期报告,并导出为PPT、Excel或PDF,适配不同管理层的信息消费习惯。上海伟诺信息科技有限公司依托多年行业积累,将YMS方案打造为兼具实用性与扩展性的国产选择。Mapping Over Ink处理系统提供售前咨询与售后标准化服务,保障客户实施体验。福建可视化GDBC解决方案

Mapping Over Ink数据处理流程全程自动化运行,大幅减少人工复核的人为干预。自动化Mapping Inkless的目的

在半导体制造中,由于Fab制程的物理与化学特性,晶圆边缘的芯片(Edge Die)其失效率明显高于中心区域。这一现象主要源于几个关键因素:首先,在光刻、刻蚀、薄膜沉积等工艺中,晶圆边缘的反应气体流场、温度场及压力场分布不均,导致工艺一致性变差;其次,边缘区域更容易出现厚度不均、残留应力集中等问题;此外,光刻胶在边缘的涂覆均匀性也通常较差。这些因素共同导致边缘芯片的电气参数漂移、性能不稳定乃至早期失效风险急剧升高。因此,在晶圆测试(CP)的制造流程中,对电性测试图谱(Wafer Mapping)执行“去边”操作,便成为一项提升产品整体良率与可靠性的关键步骤。

上海伟诺信息科技有限公司Mapping Over Ink功能中的Margin Map功能提供多种算法与自定义圈数,满足客户快速高效低剔除边缘芯片,可以从根本上避免后续对这些潜在不良品进行不必要的封装和测试,从而直接节约成本,并确保出厂产品的质量与可靠性要求。自动化Mapping Inkless的目的

上海伟诺信息科技有限公司汇集了大量的优秀人才,集企业奇思,创经济奇迹,一群有梦想有朝气的团队不断在前进的道路上开创新天地,绘画新蓝图,在上海市等地区的数码、电脑中始终保持良好的信誉,信奉着“争取每一个客户不容易,失去每一个用户很简单”的理念,市场是企业的方向,质量是企业的生命,在公司有效方针的领导下,全体上下,团结一致,共同进退,**协力把各方面工作做得更好,努力开创工作的新局面,公司的新高度,未来和您一起奔向更美好的未来,即使现在有一点小小的成绩,也不足以骄傲,过去的种种都已成为昨日我们只有总结经验,才能继续上路,让我们一起点燃新的希望,放飞新的梦想!

- 湖北可视化PAT工具 2026-04-21

- 宁夏PAT系统 2026-04-20

- 吉林MappingOverInk处理服务 2026-04-20

- 山东半导体Mapping Inkless工具 2026-04-20

- 甘肃半导体GDBC系统 2026-04-20

- 天津可视化GDBC系统 2026-04-20

- 山西半导体MappingOverInk处理系统价格 2026-04-18

- 四川自动化PAT 2026-04-18