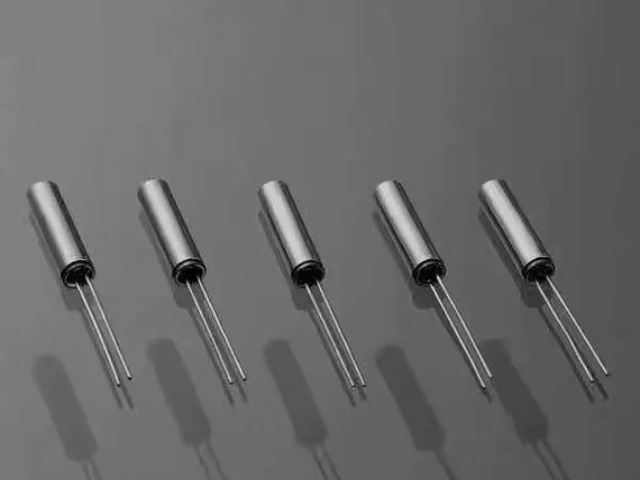

海量物联网终端设备的普及,对时钟晶振提出了微型化、低功耗、高性价比的普适性要求。数以亿计的无线传感器节点、智能标签、可穿戴设备由其内置的微控制器或低功耗无线SoC(如BLE、LoRa、NB-IoT芯片)驱动,这些芯片都需要一个主时钟晶振。物联网用时钟晶振通常工作在16MHz、26MHz、32MHz、40MHz等频率,其挑战是在极低成本和小尺寸(如2016、1612封装)下,实现足够低的功耗(工作电流常低于1mA,睡眠电流极低)和可靠的起振特性。同时,为适应大规模自动化贴装和严峻的成本压力,其设计、生产和测试流程必须高度优化。这类时钟晶振是连接物理世界与数字世界的庞大末梢网络的“基础心跳”,其可靠性与成本直接影响着物联网生态的规模与健康发展。时钟晶振的谐波需要被有效抑制。时钟晶振时钟晶振

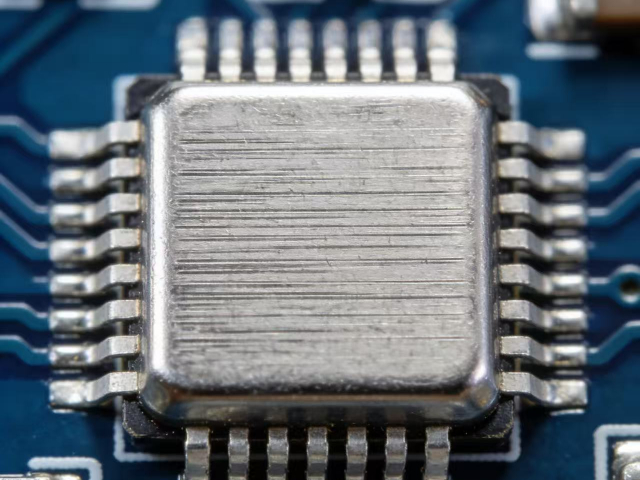

在复杂的多板卡、多芯片系统中,时钟分配网络的设计是确保全局同步的关键。此时,时钟晶振作为主时钟源,其信号需要通过时钟缓冲器、扇出驱动器或零延迟缓冲器分配到系统的各个角落。这就对时钟晶振的输出驱动能力和信号完整性提出了要求。一方面,时钟晶振需要具备足够的输出强度,以驱动后续缓冲器的输入电容和传输线的特征阻抗;另一方面,其输出信号的上升/下降时间、过冲与下冲必须得到良好控制,以防止在传输过程中产生过大的谐波辐射和反射。针对不同的负载需求,时钟晶振提供多种输出逻辑电平,如LVCMOS、LVDS、LVPECL、HCSL等。例如,LVDS输出的时钟晶振因其差分传输、低功耗、低抖动特性,常被用于驱动FPGA的高速串行收发器时钟。选择合适的输出类型,是保证时钟信号从源头到终端都保持高质量的重要一步。揭阳206封装时钟晶振价格高精度时钟晶振用于精密仪器仪表。

在电源管理日益复杂的系统中,时钟晶振有时需要与多个电源域协同工作。例如,一个时钟晶振可能同时为内核电压域和IO电压域的不同芯片提供时钟。这就涉及到了电源时序控制和电压兼容性问题。某些时钟晶振支持单独的电源(Vdd)和输出电源(VddO),允许输出电平与一个电压域匹配,而内部振荡电路工作在另一个优化的电压下,以降低整体功耗或兼容不同电平标准。在设计时,必须确保时钟晶振的电源上电顺序符合其规格书要求,通常Vdd应先于或与VddO同时上电,以防止闩锁或损坏。理解并妥善处理时钟晶振的电源需求,是多电源系统稳定启动和运行的重要一环。

时钟晶振的启动时间是影响系统上电时序、唤醒速度和故障恢复时间的重要参数。它是指从施加合规电源电压开始,到输出稳定且符合所有规格的时钟信号所需的时间。对于需要快速启动的应用,如固态硬盘的主控时钟、汽车娱乐系统的瞬时启动、或备份系统的快速切换,时钟晶振的快速启动能力(通常在几毫秒内)至关重要。启动时间与晶体谐振器的特性、振荡电路的环路增益、电源上升斜率以及是否启用省电模式有关。通过优化设计,可以在保证起振可靠性的前提下缩短启动时间。然而,在低功耗设计中,时钟晶振可能被配置为在需要时上电,此时“启动时间”与“功耗”需要权衡。一些可编程时钟晶振还支持快速锁存模式,进一步优化了频率切换或重新上电后的稳定速度。我们提供时钟晶振技术支持。

为确保时钟晶振在预期寿命内的可靠性,制造商必须执行一系列严格的环境应力筛选与寿命测试。这些测试远超出常规电性能检验,旨在模拟并加速产品在真实世界中可能遇到的恶劣条件。典型测试包括:高温存储(如125°C, 1000小时)、温度循环(-55°C至+125°C, 数百至上千次循环)、高温高湿偏压测试(85°C/85%RH, 施加额定电压)、高温工作寿命测试、机械振动(正弦/随机)、机械冲击、跌落测试以及可焊性测试。通过这些严苛测试,可以剔除早期失效产品,暴露设计或工艺缺陷,并验证产品在极端条件下的性能保持能力。对于车规、工业级时钟晶振,这些测试的条件和通过标准更为严格,是产品高可靠性的重要保证。时钟晶振的频率稳定度至关重要。揭阳206封装时钟晶振价格

时钟晶振是测量仪器精度的保证。时钟晶振时钟晶振

在多板卡、多芯片的复杂电子系统中,时钟信号的完整分配与同步是巨大挑战,而时钟晶振作为时钟树的源头,其输出信号的完整性与驱动能力至关重要。时钟晶振的输出需要驱动可能存在的传输线损耗、扇出缓冲器的输入电容以及多个远端负载。为了确保信号质量,时钟晶振需提供符合标准(如LVCMOS、LVDS、LVPECL、HCSL)且边沿速率受控的输出波形。过慢的边沿会增大串扰和开关功耗,过快的边沿则易引起振铃和电磁干扰。同时,输出振幅和共模电压必须满足接收端芯片的输入要求。在长距离或重负载场景下,可能需要时钟晶振具备较强的输出驱动电流。工程师需根据负载数量、传输距离及PCB阻抗特性,选择合适输出类型和驱动强度的时钟晶振,并通常会在其输出端实施恰当的端接策略,以抑制反射,保证到达每个接收器输入端的时钟信号干净、陡峭且无过冲。时钟晶振时钟晶振

深圳市鑫和顺科技有限公司汇集了大量的优秀人才,集企业奇思,创经济奇迹,一群有梦想有朝气的团队不断在前进的道路上开创新天地,绘画新蓝图,在广东省等地区的电子元器件中始终保持良好的信誉,信奉着“争取每一个客户不容易,失去每一个用户很简单”的理念,市场是企业的方向,质量是企业的生命,在公司有效方针的领导下,全体上下,团结一致,共同进退,**协力把各方面工作做得更好,努力开创工作的新局面,公司的新高度,未来深圳市鑫和顺科技供应和您一起奔向更美好的未来,即使现在有一点小小的成绩,也不足以骄傲,过去的种种都已成为昨日我们只有总结经验,才能继续上路,让我们一起点燃新的希望,放飞新的梦想!